Finite State Machine(FSM) เป็นตัวช่วยในการออกแบบระบบวงจรดิจิตอล โดยใช้เทคนิคเขียนแผงผังการทำงานแบบ state ซึ่งทำให้เข้าใจขั้นตอนการทำงานของระบบวงจรดิจิตอลที่จะออกแบบได้ง่ายขึ้นและทำให้การเขียนโปรแกรมด้วยภาษา VHDL(Very High Speed Intregrated Circuit Hardware Description Language) ง่ายขึ้นด้วย

การเขียน Finite State Machine ใน VHDL จะเป็นการเขียนแบบ sequential logic คือ การทำงานจะมีการเขียนเงื่อนไขตรวจสอบค่า input มีการเก็บค่าสถานะและทำการตรวจสอบเงื่อนไขอย่างต่อเนื่องซึ่งสามารถเขียนการทำงานแบบซับซ้อนหรือแบบง่ายๆ เช่น วงจร counters

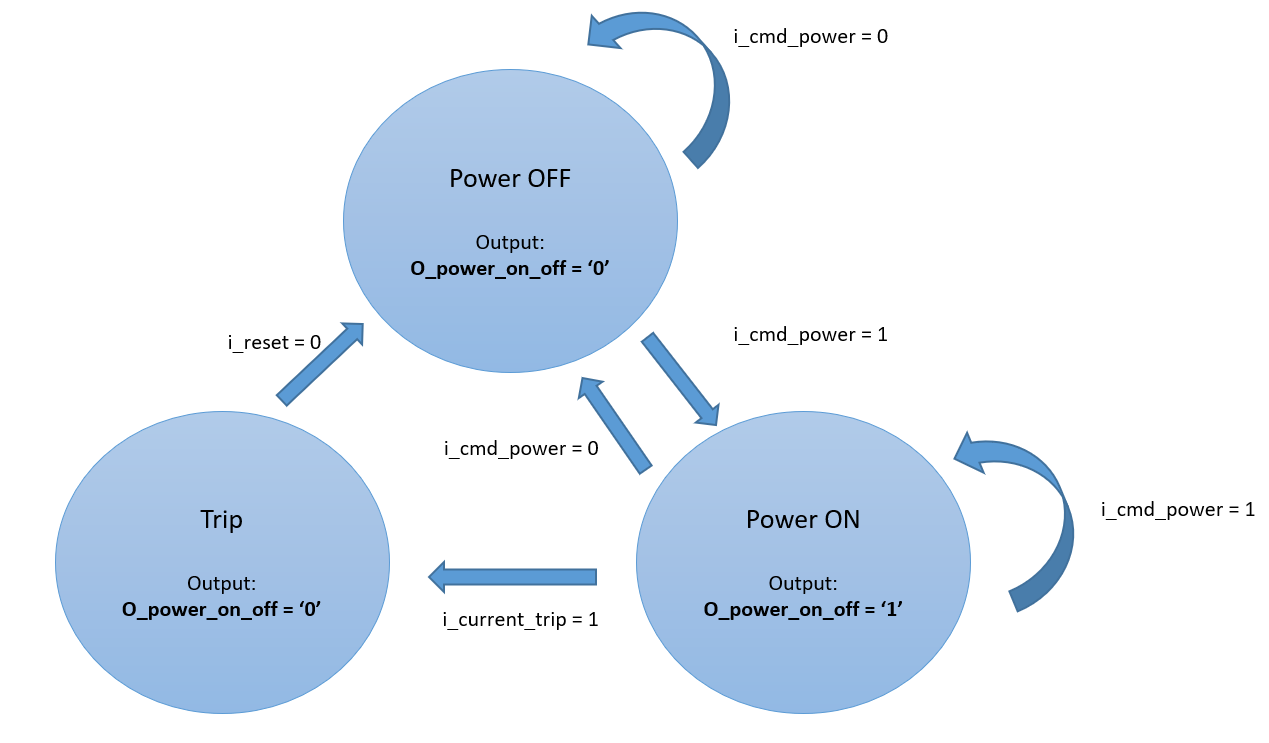

ตัวอย่างการเขียนนี้ จะทำการเขียน FSM เพื่อสร้างวงจรดิจิตอลภายใน FPGA ควบคุมการเปิด-ปิดวงจรจ่ายพลังงานซึ่งมีสัญญาณควบคุมจากวงจรป้องกันกระแสเกิน(Trip current) เป็นตัวตัดสัญญาณการเปิด-ปิดวงจรจ่ายพลังงาน

การเขียน FSM มีวิธีการดังนี้

1.กำหนดสัญญาณ input/output ให้ Blank box.

2.คิดสถานะการทำงานก่อนว่ามีอะไรบ้าง

3.เขียน Diagram FSM

4.แปลงมาเป็นภาษา VHDL

5.เขียน Test Bench เพื่อ Simulation การทำงาน

6.Implementation ใน FPGA

1. กำหนดสัญญาณ input/output ให้ Blank box.

การทำงานใน Blank Box

- สัญญาณ i_cmd_power เป็นตัวเปิด/ปิด output ถ้า i_cmd_power = 1 ที่ output o_power_on_off จะเท่ากับ 1

- แต่ถ้ามีสัญญาณ i_current_trip = ‘1’ จะตัดที่ output ทันที o_power_on_off = ‘0’ โดยสามารถควบคุมการเปิดอีกครั้งด้วยสัญญาณ i_reset = ‘0

Entity ในภาษา VHDL คือ

2. คิดสถานะการทำงานก่อนว่ามีอะไรบ้าง

คิดสถานะการทำงานโดยแบ่งการทำงานออกเป็น 3 สถานะ

1. Power Off

2. Power ON

3. Trip

3. เขียน Diagram FSM

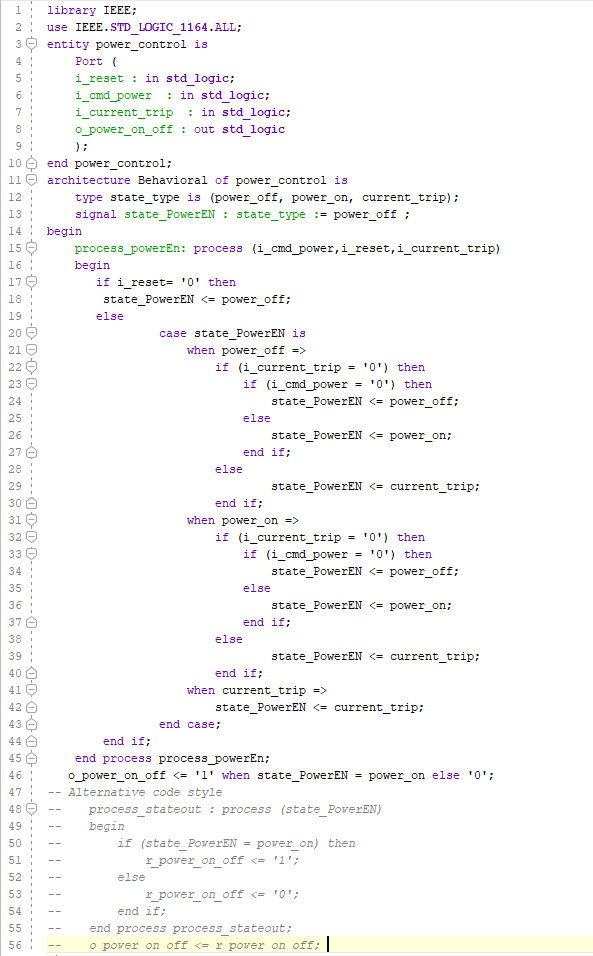

4. แปลงมาเป็นภาษา VHDL

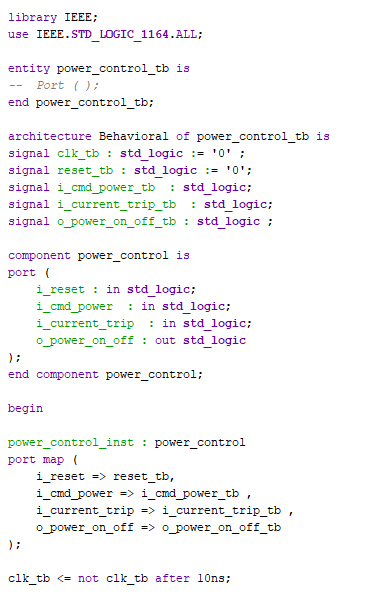

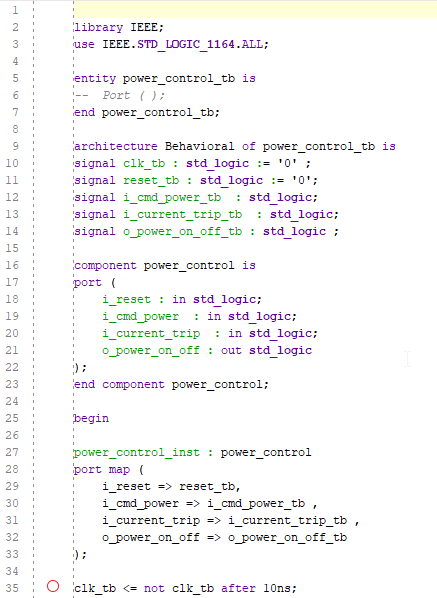

5. เขียน Test Bench เพื่อ Simulation การทำงาน

6. Implementation ใน FPGA

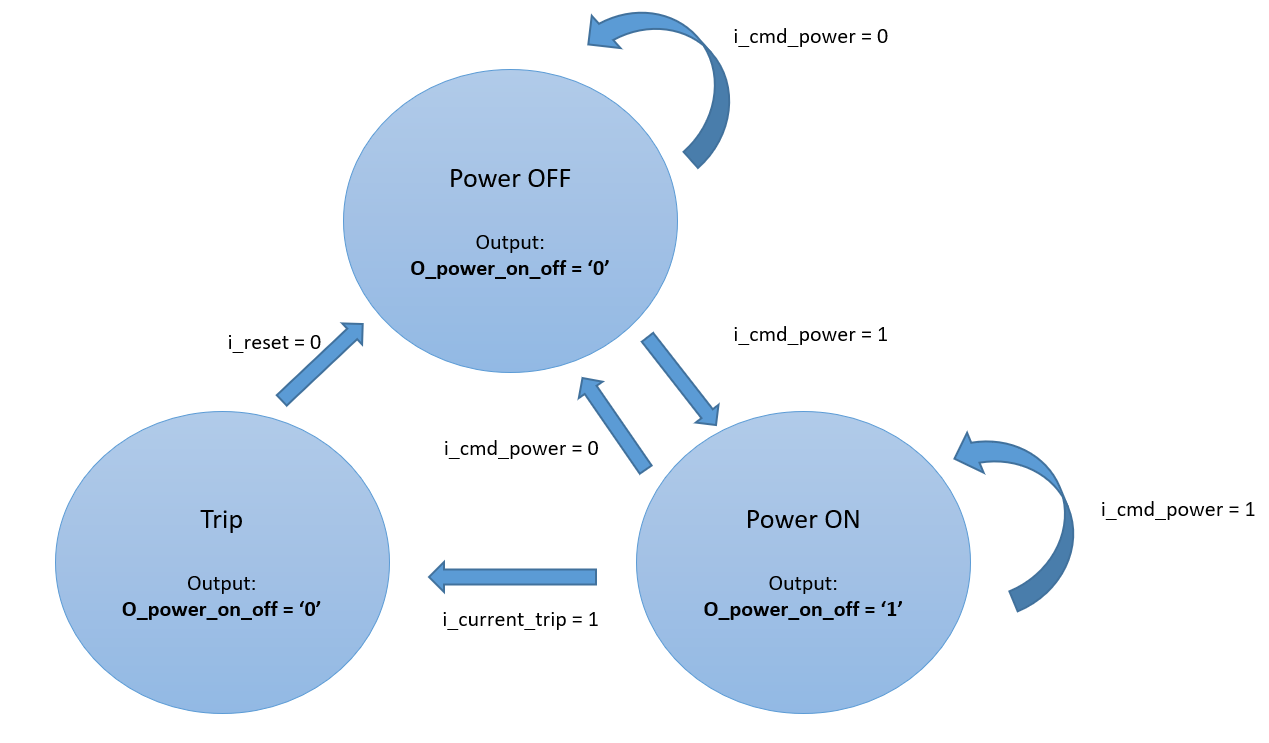

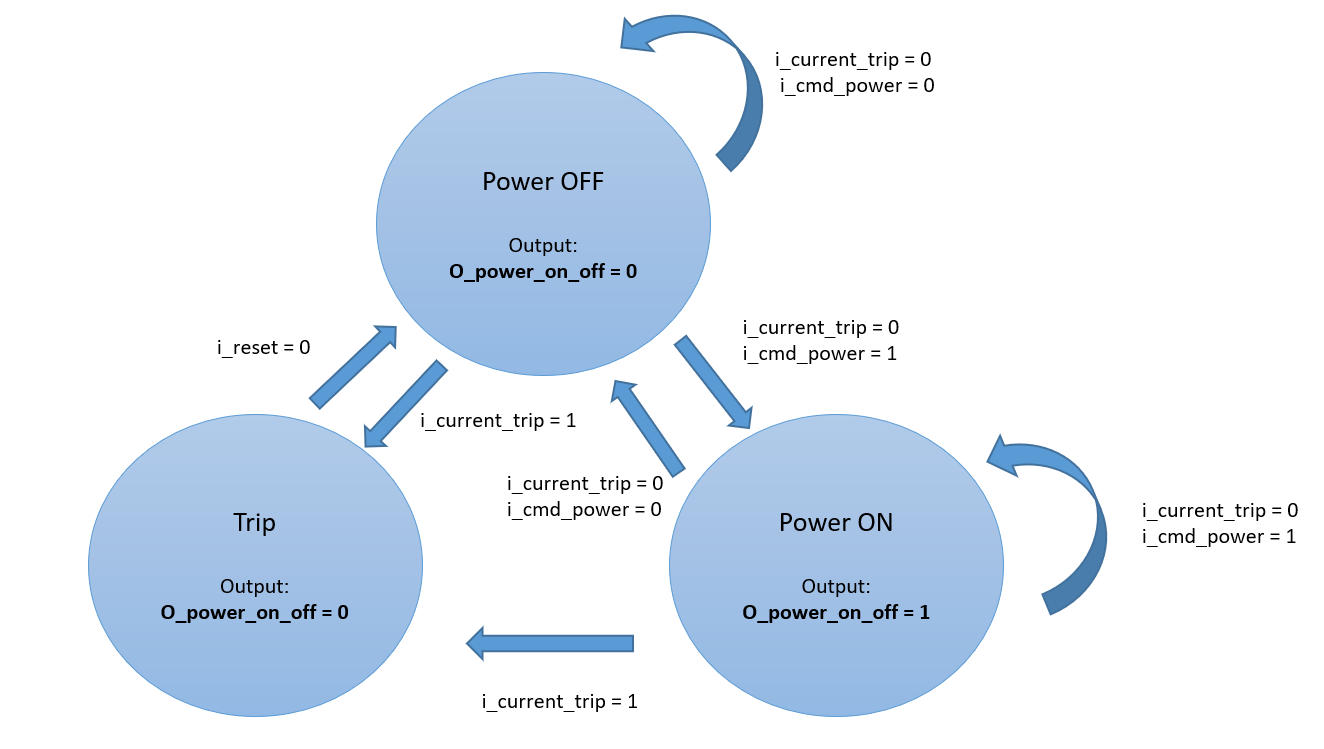

Rev2_Optimize design >> 1'st priority focus on i_current_trip if trip go to trip state

แปลงมาเป็นภาษา VHDL

Test Bench เพื่อ Simulation การทำงาน

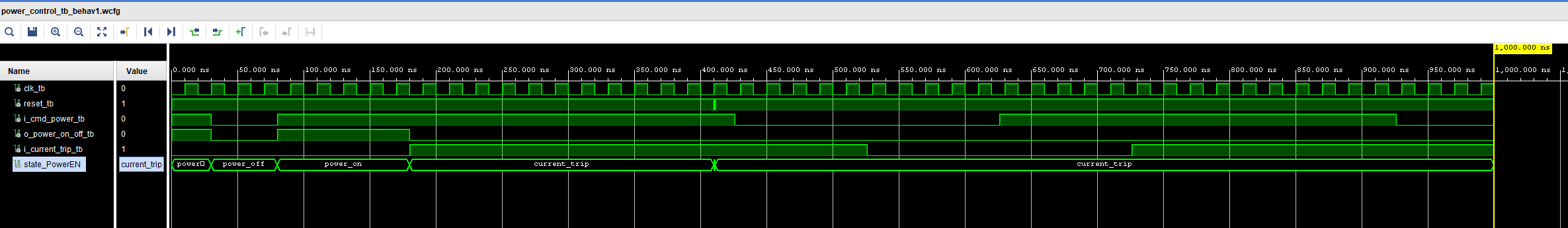

Simulation waveform

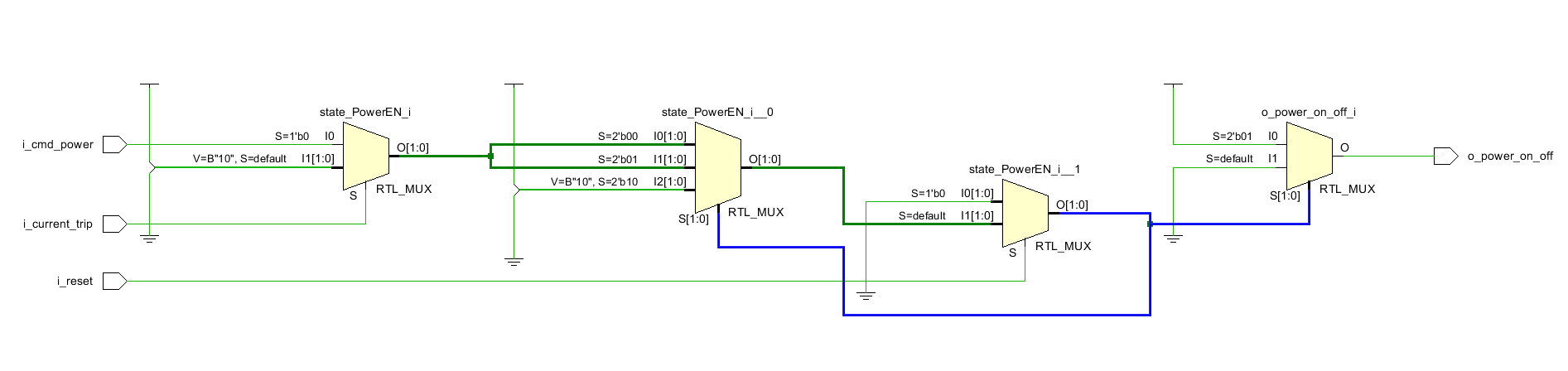

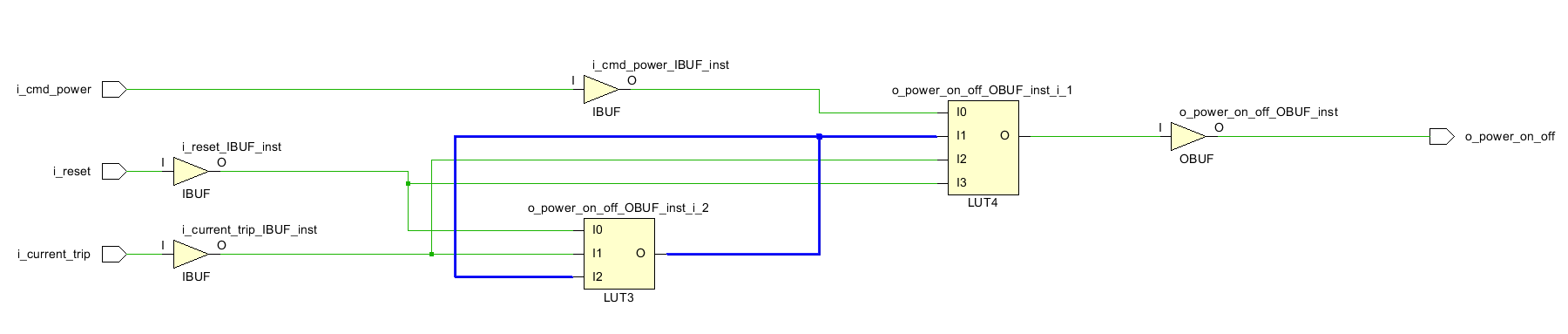

RTL Analysis: the combination loop back was created with the intention of cutting output from exceeding the current limit.

Synthesis result:

See the messages tab at the bottom of the window. we will see the warning about the combination loop.

We can fix this issue by adding allow combinational loop in the constraint file.

set_property ALLOW_COMBINATORIAL_LOOPS true [get_nets state_PowerEN[1]]

set_property SEVERITY {Warning} [get_drc_checks LUTLP-1]

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]